ABN 43 064 478 842

231 osborne avenue clayton south, vic 3169

PO box 1548, clayton south, vic 3169

t 03 9265 7400 f 03 9558 0875

freecall 1800 680 680

www.tmgtestequipment.com.au

# Test & Measurement

- sales

- rentals

- calibration

- repair

- disposal

# **Complimentary Reference Material**

This PDF has been made available as a complimentary service for you to assist in evaluating this model for your testing requirements.

TMG offers a wide range of test equipment solutions, from renting short to long term, buying refurbished and purchasing new. Financing options, such as Financial Rental, and Leasing are also available on application.

TMG will assist if you are unsure whether this model will suit your requirements.

Call TMG if you need to organise repair and/or calibrate your unit.

If you click on the "Click-to-Call" logo below, you can all us for FREE!

# Disclaimer:

All trademarks appearing within this PDF are trademarks of their respective owners.

# Detailed Product Information

# ► TLA600 and TLA700 Series Logic Analyzers.

# **TLA Family**

**Logic Analyzers**

The TLA Family of logic analyzers consists of the TLA600 Series and the TLA700 Series. The TLA600 Series offers a selection of stand-alone logic analyzer instruments at prices that make 500 ps timing resolution available to designers of today's mainstream embedded systems. The TLA700 Series offers the highest performance for today's demanding applications and consists of portable and benchtop modular mainframes with expansion mainframe capability. Instrument modules include logic analyzer, pattern generator and digital oscilloscope. A full line of complementary support products for popular processors and buses is available for the entire TLA family.

- ▶ 8 GHz MagniVu™ Acquisition Technology Provides up to 125 ps Timing Resolution on All Channels All the Time Through the Same Probe

- ▶ Up to 800 MHz State Acquisition with 1.25 Gb/s Data Rate for Advanced Processors and Buses

- ► Simultaneous State, High-speed Timing and Analog Measurement Analysis

Through the Same Probe Pinpoints Elusive Faults

- 34/68/102/136-Channel Logic Analyzers with up to 256 Mb Depth with Hardware-accelerated Waveform Display and Search Functions to Rapidly Analyze Acquired Data

- 4-Channel Digital Oscilloscope with up to 1 GHz, 5 GS/s Provides High-fidelity Signal Quality Measurements of Digital Signals

- 64-Channel Pattern Generator with up to 268 MHz and up to 2 Mb Depth Provides Stimulus for Functional Verification, Debugging and Stress Testing

- Integrated View (iView™) Capability Provides up to 6 GHz, 20 GS/s, and 32 Mb with a Stand-alone Tektronix TDS Digital Storage Oscilloscope

- ► TLAVu™ and PatGenVu™ Off-line Analysis Capability for Viewing Data and Creating Setups on a Separate PC

- Microsoft® Windows® 2000 Professional PC Platform Provides Familiar User Interface with Network Connectivity

# **Applications**

- ► Hardware Debug and Verification

- ► Processor/Bus Debug and Verification

- ► Embedded Software Integration, Debug and Verification

► Detailed Product Information

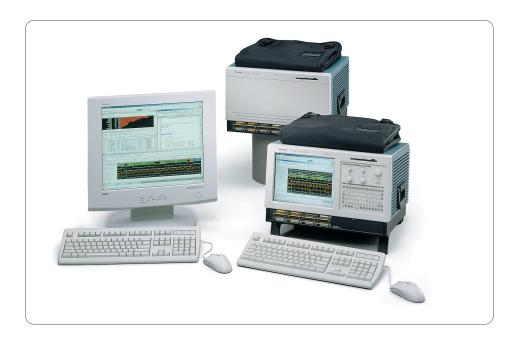

# **TLA700 Series**

Performance and Modular Flexibility for Your Toughest Design Challenges

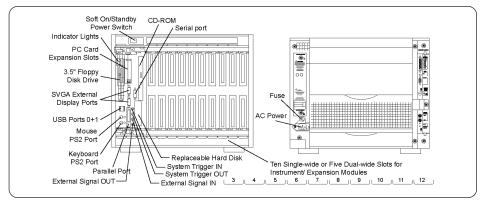

Benchtop Modular Mainframe

TLA721 with logic analyzer, pattern generator and digital oscilloscope modules

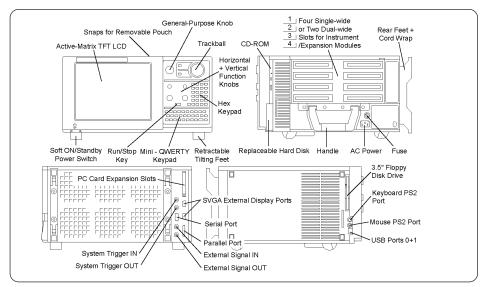

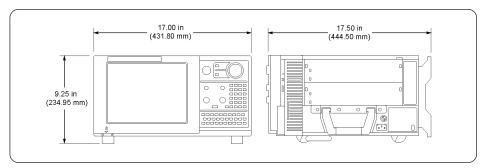

Portable Modular Mainframe

TLA715 with logic analyzer, pattern generator and digital oscilloscope modules

# **TLA600 Series**

Affordable Timing and State Logic Analyzers for Your Mainstream Design Needs

► Logic Analyzer with Internal Display TLA61x and TLA62x

► Logic Analyzer with External Display TLA60x

► Detailed Product Information

# **Table of Contents**

| Logic Analyzers                                                        |

|------------------------------------------------------------------------|

| TLA Family Selection Guide                                             |

| Tektronix Logic Analyzer Probe Selection Guide                         |

| System Overview                                                        |

| Breakthrough Solutions for Real-time Digital Systems Analysis          |

| Find and Analyze your Difficult Real-time Software Problems11          |

| Enhance Productivity through Familiarity,  Connectivity and Modularity |

# Characteristics TLA7Dx/Ex Digital Storage Ordering Information TLA7Dx/Ex Digital Storage TLA Family Service Options .......43

► Detailed Product Information

# **TLA Family Selection Guide**

| Applications                         |    | TLA6xx                                      | TLA715                           | 5                        | TLA721    |             |

|--------------------------------------|----|---------------------------------------------|----------------------------------|--------------------------|-----------|-------------|

| Timing and State Analysis            |    | Yes                                         | Yes                              |                          | Yes       |             |

| Single-processor/Bus Analysis        |    | Yes                                         | Yes                              |                          | Yes       |             |

| Real-time Instruction Trace Analysis |    | Yes                                         | Yes                              |                          | Yes       |             |

| Source Code Debug                    |    | Yes                                         | Yes                              |                          | Yes       |             |

| Performance Analysis                 |    | Yes                                         | Yes                              |                          | Yes       |             |

| Multi-processor/Bus Analysis         |    | -                                           | Yes                              |                          | Yes       |             |

| Digital Stimulus and Control         |    | -                                           | Yes                              |                          | Yes       |             |

| Digital Signal Quality Analysis      |    | Yes                                         | Yes                              |                          | Yes       |             |

| System Validation                    |    | -                                           | _                                |                          | Yes       |             |

| TLA Mainframe Selection              | Т  | TLA6xx                                      | TLA715                           | TLA721                   | TLA       | A7XM        |

| Type of Mainframe                    | No | n-modular                                   | Modular                          | Modular                  | Expansion | n – Modular |

| Number of Module Slots               |    | N/A                                         | 2                                | 5                        |           | 6           |

| Operating System                     |    | Micros                                      | rosoft Windows 2000 Professional |                          | 1         | V/A         |

| Internal Display Resolution          |    | (TLA61x/62x only;<br>ires external display) | 800x600                          | Requires external displa | ıy N      | V/A         |

| External Display Resolution          | 12 | 280x1024                                    | 1600x1200                        | 1600x1200                | ı         | N/A         |

| Number of External Displays          |    | 1                                           | 4 (with two                      | 4 (with two              | 1         | J/Δ         |

| Operating System                       | Micros                                                         | soft Windows 2000 Profession       | al                                 | N/A |

|----------------------------------------|----------------------------------------------------------------|------------------------------------|------------------------------------|-----|

| Internal Display Resolution            | 800x600 (TLA61x/62x only;<br>TLA60x requires external display) | 800x600                            | Requires external display          | N/A |

| External Display Resolution            | 1280x1024                                                      | 1600x1200                          | 1600x1200                          | N/A |

| Number of External Displays            | 1                                                              | 4 (with two PCMCIA video adapters) | 4 (with two PCMCIA video adapters) | N/A |

| Standard Data Window Types             | Waveform, Listing                                              | , Histogram (Performance Ana       | alysis), Source Code               | N/A |

| Remote Control with Microsoft COM/DCOM | Yes                                                            | Yes                                | Yes                                | N/A |

| TLA Logic Analyzer Selection                        | TLA6xx                            | TLA7Nx/Px/Qx                                                               | TLA7Axx                                                                    |

|-----------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Channels                                            | 34, 68, 102, 136 per instrument   | 34, 68, 102, 136 per module                                                | 34, 68, 102, 136 per module                                                |

| Max Channels per Timebase (merged)                  | 136                               | 272 in TLA715<br>408 in TLA721                                             | 272 in TLA715<br>680 in TLA721                                             |

| Max Channels per Mainframe                          | 136                               | 272 in TLA715<br>680 in TLA721                                             | 272 in TLA715<br>680 in TLA721                                             |

| Max Channels per System                             | 136                               | 1,768 (with TLA715 and two TLA7XMs)<br>8,160 (with TLA721 and ten TLA7XMs) | 1,768 (with TLA715 and two TLA7XMs)<br>8,160 (with TLA721 and ten TLA7XMs) |

| Max Independent Buses per System                    | 1                                 | 13 (with TLA715 and two TLA7XMs)<br>60 (with TLA721 and ten TLA7XMs)       | 13 (with TLA715 and two TLA7XMs)<br>60 (with TLA721 and ten TLA7XMs)       |

| State Clock Rate                                    | 100 MHz std.<br>200 MHz opt.      | 100 MHz std.<br>200 MHz opt.                                               | 120 MHz std.<br>235, 450 MHz opt.                                          |

| Max State Clock Rate (half channel mode)            | 200 MHz                           | 200 MHz                                                                    | 800 MHz                                                                    |

| Max State Data Rate                                 | 400/200 Mb/s (half/full channels) | 400/200 Mb/s (half/full channels)                                          | 1,250/900/450 Mb/s<br>(quarter/half/full channels)                         |

| MagniVu Timing (all channels, all the time)         | 2 GHz (500 ps) with 2 Kb depth    | 2 GHz (500 ps) with 2 Kb depth                                             | 8 GHz (125 ps) with 16 Kb depth                                            |

| Simultaneous State and Timing<br>Through Same Probe | Yes                               | Yes                                                                        | Yes                                                                        |

| Analog Measurements Through Same Probe              | No                                | No                                                                         | Yes                                                                        |

# Tektronix Logic Analyzers ▶ Detailed Product Information

| TLA Logic Analyzer Selection (cont.)             | TL                                                      | A6xx                                                                  | X TLA7Nx/Px/Qx                                                        |                             | TLA7Axx                                                              |  |

|--------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------|----------------------------------------------------------------------|--|

| Deep Timing                                      | 500 MHz (2 ns)/250 MHz (4 ns)<br>(half/full channels)   |                                                                       | 500 MHz (2 ns)/250 MHz (4 ns)<br>(half/full channels)                 |                             | 2 GHz (500 ps)/1 GHz (1 ns)/500 M<br>(quarter/half/full channels)    |  |

| Memory Depth                                     | 128/64 Kb to 2/1 Mb (half/full channels with timestamp) |                                                                       | 128/64 Kb to 128/64 Mb<br>(half/full channels with timestamp)         |                             | 512/256/128 Kb to 256/128/6-<br>(quarter/half/full channels with tim |  |

| Source Synchronous Clocking                      |                                                         | No                                                                    |                                                                       | No                          | Yes                                                                  |  |

| Analog Outputs<br>(four per module – analog MUX) |                                                         | No                                                                    | No                                                                    |                             | Yes                                                                  |  |

| Digital Storage Oscilloscope Capabilit           | ty                                                      | TLA7Dx/Ex Mod                                                         | dules (Internal)                                                      | TDS Oscillo                 | oscopes*1 (External)                                                 |  |

| Channels per Module                              |                                                         | 2 &                                                                   | . 4                                                                   |                             | 2 & 4                                                                |  |

| Max Channels per Mainframe                       |                                                         | 8 (TLA<br>20 (TL/                                                     | ,                                                                     |                             | 4                                                                    |  |

| ' '                                              |                                                         | 52 (with TLA715 and two TLA7XMs)<br>240 (with TLA721 and ten TLA7XMs) |                                                                       | 4                           |                                                                      |  |

| Bandwidth                                        |                                                         | 500 MHz & 1 GHz                                                       |                                                                       | 10                          | 100 MHz to 6 GHz                                                     |  |

| Sample Rate                                      |                                                         | 2.5 GS/s & 5 GS/s 1                                                   |                                                                       | 1.25                        | GS/s to 20 GS/s                                                      |  |

| Vertical Resolution                              |                                                         | 8-B                                                                   | its                                                                   | 8-                          | Bits and 9-Bits                                                      |  |

| Memory Depth                                     |                                                         | 15                                                                    | Kb                                                                    | 1                           | Kb to 32 Mb                                                          |  |

| TLA Pattern Generator Module                     |                                                         |                                                                       | TL                                                                    | A7PG2                       |                                                                      |  |

| Channels                                         |                                                         |                                                                       | 64                                                                    |                             |                                                                      |  |

| Max Channels per Bus (merged)                    |                                                         |                                                                       | 128 (with TLA715) 320 (with TLA721)                                   |                             |                                                                      |  |

| Max Channels per Mainframe                       |                                                         |                                                                       | 128 (with TLA715) 320 (with TLA721)                                   |                             |                                                                      |  |

| Max Channels per System                          | Channels per System                                     |                                                                       | 832 (with TLA715 and two TLA7XMs) 3,840 (with TLA721 and ten TLA7XMs) |                             |                                                                      |  |

| Pattern Speed (half/full channels)               |                                                         |                                                                       | 268/134 MHz                                                           |                             |                                                                      |  |

| Memory Depth (half/full channels)                |                                                         | 512 / 256 Kb to 2 / 1 Mb                                              |                                                                       |                             |                                                                      |  |

| Logic Families Supported                         |                                                         | CMC                                                                   | OS/TTL, ECL, LVCMOS                                                   | S, PECL/LVPECL, LVDS, Varia | ble                                                                  |  |

<sup>\*1</sup> For a complete list of currently supported TDS oscilloscopes, please visit our website http://www.tektronix.com/iview.

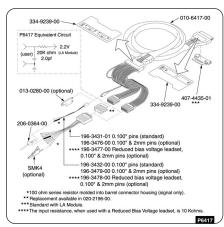

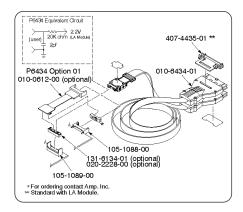

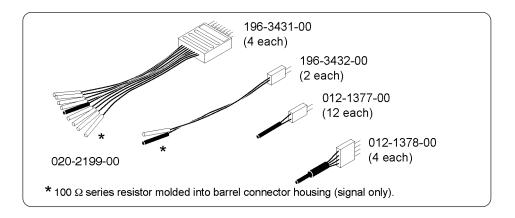

# **Tektronix Logic Analyzer Probe Selection Guide**

|                                                                          | P6810                                                                                                                                   | P6860                                                                                                                                                                               | P6880                                                                                                                                                                               | P6417                                                                                                                 | P6418                                                                                                                 | P6434                                                                                                                                     |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Logic Analyzer Used                                                      |                                                                                                                                         | 7AAx Logic Analyzer Moo<br>7ABx Logic Analyzer Moo                                                                                                                                  |                                                                                                                                                                                     | TLA7L                                                                                                                 | TLA6xx Logic Analyzers<br>x/7Mx Logic Analyzer M<br>7Px/7Qx Logic Analyzer                                            |                                                                                                                                           |

| Recommended Use                                                          | Recommended for<br>most general-purpose<br>uses that require<br>maximum flexibility for<br>single-ended or<br>differential requirements | quickly connected in                                                                                                                                                                | Recommended for<br>applications requiring<br>many differential<br>channels to be<br>quickly connected in<br>a small footprint                                                       | Recommended<br>for most<br>general-purpose<br>uses that require<br>maximum flexibility                                | Recommended<br>for most<br>general-purpose<br>uses                                                                    | Recommended for<br>applications<br>requiring many<br>channels to be<br>quickly connected in<br>a small footprint                          |

| Attachment to Target System                                              | Probe leadsets<br>adapt to industry<br>standard interfaces;<br>leads spread over<br>a wide area                                         | Connectorless<br>"compression" contact<br>(Adapter for<br>Mictor connector<br>available)                                                                                            | Connectorless<br>"compression" contact<br>(Adapter for<br>Mictor connector<br>available)                                                                                            | Probe leadsets<br>adapt to industry<br>standard interfaces;<br>leads spread over<br>a wide area                       | Probe leadsets<br>adapt to industry<br>standard interfaces                                                            | AMP Mictor 34-<br>channel connector<br>(Adapter to use P6434<br>with P6860/80<br>high-density<br>compression land<br>footprint available) |

| Probe Type                                                               | General-purpose,<br>34-channel<br>active probe                                                                                          | High-density,<br>34-channel<br>active probe                                                                                                                                         | High-density,<br>34-channel<br>active differential<br>probe                                                                                                                         | General-purpose,<br>17-channel<br>passive probe                                                                       | General-purpose,<br>17-channel<br>passive probe                                                                       | High-density,<br>34-channel<br>passive probe<br>AMP Mictor<br>connector required                                                          |

| Pin Spacing Supported                                                    | 0.100 in. and 2 mm                                                                                                                      | N/A                                                                                                                                                                                 | N/A                                                                                                                                                                                 | 0.100 in.                                                                                                             | 0.100 in.                                                                                                             | N/A                                                                                                                                       |

| Logic Signals Supported                                                  | Differential Clock<br>Differential Data                                                                                                 | Differential Clock<br>Single-ended Data                                                                                                                                             | Differential Clock<br>Differential Data                                                                                                                                             | Single-ended Clock<br>and Data (Differential<br>signal adapters<br>available)                                         | Single-ended Clock<br>and Data (Differential<br>signal adapters<br>available)                                         | Single-ended Clock<br>and Data                                                                                                            |

| Simultaneous State/<br>Timing to:                                        | 800 MHz/<br>8 GHz                                                                                                                       | 800 MHz/<br>8 GHz                                                                                                                                                                   | 800 MHz/<br>8 GHz                                                                                                                                                                   | 200 MHz/<br>2 GHz                                                                                                     | 200 MHz/<br>2 GHz                                                                                                     | 200 MHz/<br>2 GHz                                                                                                                         |

| Simultaneous State/<br>Timing/Analog to:                                 | 800 MHz/<br>8 GHz/2 GHz                                                                                                                 | 800 MHz/<br>8 GHz/2 GHz                                                                                                                                                             | 800 MHz/<br>8 GHz/2 GHz                                                                                                                                                             | N/A                                                                                                                   | N/A                                                                                                                   | N/A                                                                                                                                       |

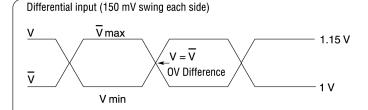

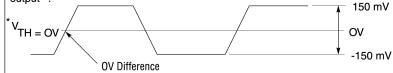

| Minimum Signal Amplitude<br>Minimum Single-ended<br>Minimum Differential | $300~\text{mV}_{\text{p-p}}$ $\text{V}_{\text{max}}-\text{V}_{\text{min}}\!\geq\!150~\text{mV}$                                         | $300~\text{mV}_{\text{p-p}} \\ \text{V}_{\text{max}} - \text{V}_{\text{min}} \ge 150~\text{mV}$                                                                                     | $300~\text{mV}_{\text{p-p}} \\ \text{V}_{\text{max}} - \text{V}_{\text{min}} \ge 150~\text{mV}$                                                                                     | 500 mV <sub>p-p</sub><br>N/A                                                                                          | 500 mV <sub>p-p</sub><br>N/A                                                                                          | 500 mV <sub>p-p</sub><br>N/A                                                                                                              |

| Probe Load AC/DC                                                         | 1.2 pF/20 kΩ<br>to Ground                                                                                                               | 0.7 pF/20 kΩ<br>to Ground                                                                                                                                                           | 0.7 pF/20 kΩ<br>to Ground                                                                                                                                                           | 2 pF/20 kΩ<br>to 2.2 V<br>(Low-voltage adapters<br>that work with<br>low-voltage signals<br>are available)            | 2 pF/20 kΩ<br>to 2.2 V<br>(Low-voltage adapters<br>that work with<br>low-voltage signals<br>are available)            | 2 pF/20 kΩ<br>to 2.2 V                                                                                                                    |

| Notes                                                                    | Works with a<br>wide range of<br>industry-standard<br>accessories for<br>flexible attachment<br>to your target system                   | No connector required:<br>only land pads<br>required to be laid<br>out on target system<br>PCB for 17 and/or<br>34 channels.<br>Please refer to<br>P6860/6880 probe<br>design guide | No connector required:<br>only land pads<br>required to be laid<br>out on target system<br>PCB for 17 and/or<br>34 channels.<br>Please refer to<br>P6860/6880 probe<br>design guide | Works with a<br>wide range of<br>industry-standard<br>accessories for<br>flexible attachment<br>to your target system | Works with a<br>wide range of<br>industry-standard<br>accessories for<br>flexible attachment<br>to your target system | Requires AMP Mictor connector to be installed on target system PCB for every 34 channels. Please refer to P6434 probe manual              |

# **System Overview - Features and Benefits**

# System Capability

| Flexible Acquisition and Stimulus                                                                                                                                | - TLA600 Series offers similar measurement capability as modular series in fixed channel widths for mainstream digital designers.                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Logic Analyzer Acquisition Modules</li> <li>Digital Oscilloscope Modules</li> <li>Pattern Generator Modules</li> <li>Integrated View (iView)</li> </ul> | <ul> <li>TLA700 Series modular approach allows you to select the optimum combination of stimulus and acquisition to fit your<br/>performance, feature, and budget requirements.</li> </ul>                                                                      |

|                                                                                                                                                                  | <ul> <li>System software, setup information, data files common to both TLA600 and TLA700 instruments enabling easy data and file<br/>sharing between groups or instruments.</li> </ul>                                                                          |

|                                                                                                                                                                  | <ul> <li>Real-time correlated data views provide system level visibility from high-level source code to high-speed state &amp; timing to analog<br/>characteristics of digital signals.</li> </ul>                                                              |

|                                                                                                                                                                  | - Utilize industry leading TDS oscilloscopes to view time-correlated analog and digital data in the same TLA display.                                                                                                                                           |

| Enhanced TLA700 Mainframe Hardware                                                                                                                               | - Pentium® III processor, with up to 60 GB hard disk, 512 MB system RAM, and CDRW provides a powerful platform for data analysis.                                                                                                                               |

|                                                                                                                                                                  | - Multiple monitor support, each with up to 1600 x 1200 resolution, to see more data.                                                                                                                                                                           |

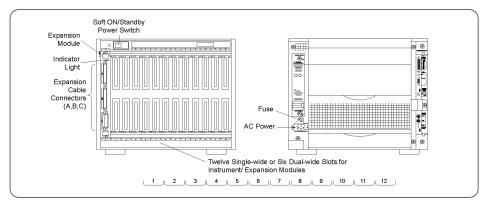

| Expansion Capability                                                                                                                                             | <ul> <li>By connecting up to 10 expansion mainframes you can simultaneously view time-correlated data for multi-bus designs (up to 60 individual buses) using up to 8160 channels, each with up to 256 Mb memory depth.</li> </ul>                              |

| TLAVu, PatGenVu Offline Analysis                                                                                                                                 | - Utilize this free application software to analyze data or create setups on a separate PC.                                                                                                                                                                     |

| Upgrade, trade-in capability                                                                                                                                     | <ul> <li>Upgrade kits offer upgrades to system RAM, hard disk, TLA application software, operating system software, iView capability and<br/>controllers to help protect investments and allow test equipment to change as measurement needs change.</li> </ul> |

|                                                                                                                                                                  | <ul> <li>PowerFlex™ program provides customer installable upgrades on measurement modules including faster state speed and additional<br/>memory depth to allow the flexibility to upgrade instrumentation over time.</li> </ul>                                |

|                                                                                                                                                                  | - Mainframe and module trade-in programs protect investments by providing discounts on future measurement equipment.                                                                                                                                            |

# Measurement Modules and Key Interface Features

| provide enough power to capture and debug the fastest and most complex high-speed digital designs.  TLA7Nx/Px/Qx Logic Analyzer Modules  - 2 GHz MagniVu timing, 100 to 200 MHz state acquisition (up to 400 Mb/s data rate), and 64 Kb to 128 Mb memory depth capability provide the tools necessary to address a wide range of digital designs.  - 2 GHz MagniVu timing, 100 to 200 MHz state acquisition (up to 400 Mb/s data rate), and 64 Kb to 2 Mb memory depth capab provide analysis tools to address mainstream digital design and debug.  - 500 MHz and 1 GHz, 2.5 and 5 GS/s, 2 and 4 channel oscilloscope modules provide analog trace capture time-correlated with digital data.  - 64 Channel, up to 268 MHz, and up to 2 Mb vector depth along with probes supporting multiple logic levels and variable delay provides a flexible solution for device simulation and hardware verification.  - Up to 6 GHz, 20 GS/s, 4 channel TDS oscilloscope data automatically time-correlated with TLA digital data on the logic analyzed display.  - Route any four logic analyzer input channels to the four analog signal output BNC connectors on the TLA7Axx module. Connecting internal oscilloscope module or external TDS oscilloscope to view analog signal information.  - Analog signal outputs are always active allowing visibility of analog information at all times.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                        |                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| capability provide the tools necessary to address a wide range of digital designs.  TLA6xx Logic Analyzers  - 2 GHz MagniVu timing, 100 to 200 MHz state acquisition (up to 400 Mb/s data rate), and 64 Kb to 2 Mb memory depth capab provide analysis tools to address mainstream digital design and debug.  TLA7Dx/Ex Digital Oscilloscope Modules  - 500 MHz and 1 GHz, 2.5 and 5 GS/s, 2 and 4 channel oscilloscope modules provide analog trace capture time-correlated with digital data.  TLA7PG2 Pattern Generator Module  - 64 Channel, up to 268 MHz, and up to 2 Mb vector depth along with probes supporting multiple logic levels and variable delay provides a flexible solution for device simulation and hardware verification.  Integrated View (iView)  - Up to 6 GHz, 20 GS/s, 4 channel TDS oscilloscope data automatically time-correlated with TLA digital data on the logic analyzed display.  - Route any four logic analyzer input channels to the four analog signal output BNC connectors on the TLA7Axx module. Connectiniternal oscilloscope module or external TDS oscilloscope to view analog signal information.  - Analog signal outputs are always active allowing visibility of analog information at all times.  MagniVu Technology  - MagniVu acquisition technology provides up to 125 ps timing resolution simultaneous with state acquisition on all channels all                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | TLA7Axx Logic Analyzer Modules         | <ul> <li>8 GHz MagniVu<sup>™</sup> timing, 120 to 800 MHz state acquisition (up to 1.25 Gb/s data rate), 128 Kb to 256 Mb memory depth capability provide enough power to capture and debug the fastest and most complex high-speed digital designs.</li> </ul> |

| provide analysis tools to address mainstream digital design and debug.  TLA7Dx/Ex Digital Oscilloscope Modules  - 500 MHz and 1 GHz, 2.5 and 5 GS/s, 2 and 4 channel oscilloscope modules provide analog trace capture time-correlated with digital data.  TLA7PG2 Pattern Generator Module  - 64 Channel, up to 268 MHz, and up to 2 Mb vector depth along with probes supporting multiple logic levels and variable delay provides a flexible solution for device simulation and hardware verification.  - Up to 6 GHz, 20 GS/s, 4 channel TDS oscilloscope data automatically time-correlated with TLA digital data on the logic analyzed display.  - Route any four logic analyzer input channels to the four analog signal output BNC connectors on the TLA7Axx module. Connecting internal oscilloscope module or external TDS oscilloscope to view analog signal information.  - Analog signal outputs are always active allowing visibility of analog information at all times.  MagniVu Technology  - Magnivu acquisition technology provides up to 125 ps timing resolution simultaneous with state acquisition on all channels all times.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TLA7Nx/Px/Qx Logic Analyzer Modules    |                                                                                                                                                                                                                                                                 |

| digital data.  TLA7PG2 Pattern Generator Module  - 64 Channel, up to 268 MHz, and up to 2 Mb vector depth along with probes supporting multiple logic levels and variable delay provides a flexible solution for device simulation and hardware verification.  - Up to 6 GHz, 20 GS/s, 4 channel TDS oscilloscope data automatically time-correlated with TLA digital data on the logic analyzed display.  - Route any four logic analyzer input channels to the four analog signal output BNC connectors on the TLA7Axx module. Connecting internal oscilloscope module or external TDS oscilloscope to view analog signal information.  - Analog signal outputs are always active allowing visibility of analog information at all times.  MagniVu Technology  - MagniVu acquisition technology provides up to 125 ps timing resolution simultaneous with state acquisition on all channels all                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TLA6xx Logic Analyzers                 | <ul> <li>2 GHz MagniVu timing, 100 to 200 MHz state acquisition (up to 400 Mb/s data rate), and 64 Kb to 2 Mb memory depth capability provide analysis tools to address mainstream digital design and debug.</li> </ul>                                         |

| provides a flexible solution for device simulation and hardware verification.  - Up to 6 GHz, 20 GS/s, 4 channel TDS oscilloscope data automatically time-correlated with TLA digital data on the logic analyzer display.  - Route any four logic analyzer input channels to the four analog signal output BNC connectors on the TLA7Axx module. Connect internal oscilloscope module or external TDS oscilloscope to view analog signal information.  - Analog signal outputs are always active allowing visibility of analog information at all times.  MagniVu Technology  - MagniVu acquisition technology provides up to 125 ps timing resolution simultaneous with state acquisition on all channels all                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TLA7Dx/Ex Digital Oscilloscope Modules | - 500 MHz and 1 GHz, 2.5 and 5 GS/s, 2 and 4 channel oscilloscope modules provide analog trace capture time-correlated with digital data.                                                                                                                       |

| display.  - Route any four logic analyzer input channels to the four analog signal output BNC connectors on the TLA7Axx module. Connectors on | TLA7PG2 Pattern Generator Module       | <ul> <li>64 Channel, up to 268 MHz, and up to 2 Mb vector depth along with probes supporting multiple logic levels and variable delays<br/>provides a flexible solution for device simulation and hardware verification.</li> </ul>                             |

| internal oscilloscope module or external TDS oscilloscope to view analog signal information.  - Analog signal outputs are always active allowing visibility of analog information at all times.  - MagniVu Technology  - MagniVu acquisition technology provides up to 125 ps timing resolution simultaneous with state acquisition on all channels all                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Integrated View (iView)                | <ul> <li>Up to 6 GHz, 20 GS/s, 4 channel TDS oscilloscope data automatically time-correlated with TLA digital data on the logic analyzer<br/>display.</li> </ul>                                                                                                |

| MagniVu Technology — MagniVu acquisition technology provides up to 125 ps timing resolution simultaneous with state acquisition on all channels at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                        | <ul> <li>Route any four logic analyzer input channels to the four analog signal output BNC connectors on the TLA7Axx module. Connect an internal oscilloscope module or external TDS oscilloscope to view analog signal information.</li> </ul>                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                        | - Analog signal outputs are always active allowing visibility of analog information at all times.                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MagniVu Technology                     | <ul> <li>MagniVu acquisition technology provides up to 125 ps timing resolution simultaneous with state acquisition on all channels all<br/>the time.</li> </ul>                                                                                                |

► Detailed Product Information

# Measurement Modules and Key Interface Features (cont.)

| - Graphical and textual trigger descriptions to easily define a trace event.                                                  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| - Trigger interface quickly sets up the powerful trigger state machine to save time in debug efforts.                         |  |  |  |

| - Over 100 pre-defined categorized trigger programs to choose from.                                                           |  |  |  |

| - Programmable trigger interface for creating specialized triggers to aid in tracking down elusive problems.                  |  |  |  |

| - State-based trigger machine with 16 states available to aid in finding complex problems in digital designs.                 |  |  |  |

| - Decrement counters.                                                                                                         |  |  |  |

| - 16 transition recognizers.                                                                                                  |  |  |  |

| - "Snapshot" trigger that loads a current state on the fly for use later in a trigger program.                                |  |  |  |

| - Separate MagniVu™ trigger action to view high-speed timing information where it is needed most.                             |  |  |  |

| - Acquire real-time trace of processor or bus cycles without interfering with bus operation.                                  |  |  |  |

| - High-level source code analysis correlates high-level language with real-time trace.                                        |  |  |  |

| - Symbolic debug with unlimited number of symbols. Object file formats supported include IEEE695, OMF51/86/166/286/386, COFF, |  |  |  |

| Elf/Dwarf 1 & 2, Elf/Stabs, and TSF (Tektronix Symbol Format).                                                                |  |  |  |

| - Monitor and correlate multiple processors or buses simultaneously with the TLA700 series logic analyzer.                    |  |  |  |

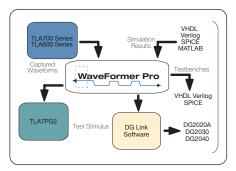

| - Use captured logic analysis data to generate simulation vectors.                                                            |  |  |  |

| - Easily perform hardware verification by comparing captured data with simulation data.                                       |  |  |  |

|                                                                                                                               |  |  |  |

# Documentation, Remote Programming

| Documentation Capability                               | - Utilize the pre-installed Snaglt™ graphical capture software to save graphics as TIF, PCX, JPG, BMP, GIF files or send them directly |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

|                                                        | to a local or networked printer.                                                                                                       |

|                                                        | - Capture any window, region, or object on the screen.                                                                                 |

|                                                        | - Start Snaglt directly from the TLA application software.                                                                             |

| Data Export                                            | - Export data in ASCII, binary, or Tektronix .tla file formats for offline use.                                                        |

| Remote Programming with Microsoft's COM/DCOM Interface | - Control logic analyzer operation using TLA Programmatic Interface (TPI) providing automated operation of the TLA.                    |

# TLA Application Software

| Microsoft Windows 2000 Professional | - Open Windows interface provides a familiar user interface and network connectivity.                                           |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

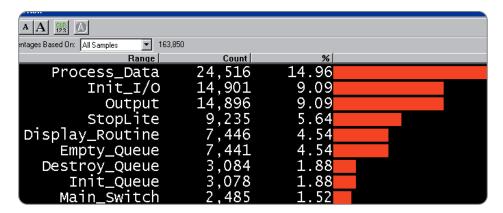

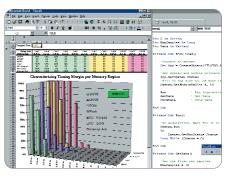

| Multiple Analysis Windows           | - View data in waveform, listing, source, or histogram windows to better analyzer cross-domain data from a target system.       |

|                                     | - Lock multiple windows of data together for improved analysis of correlated data.                                              |

| Global Cursors and Marks            | - Utilize multiple cursors and user-definable marks to aid in the analysis of data across multiple data windows.                |

|                                     | - Lock cursors together in data windows providing constant offsets to make measurements quickly.                                |

| Flexible Data Views                 | - Quickly zoom in on areas of interest, resize waveforms, overlay analog and digital waveforms, make analog measurements, label |

|                                     | waveforms, and color code symbols to customize the display for easy analysis of complex digital systems.                        |

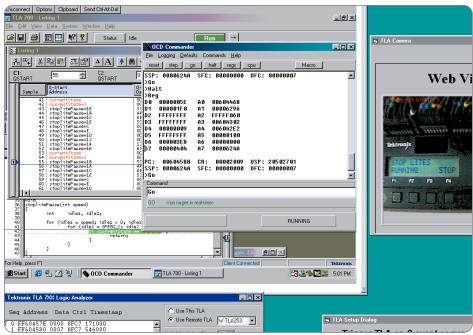

| Web-Enabled System                  | - Quickly and easily run a TLA over a network from a workstation or over the Internet.                                          |

|                                     | - Transfer data over the network for offline analysis using TLAVu.                                                              |

| Network Security                    | - Utilize the built-in security of Windows 2000 Professional to protect the data integrity of your files.                       |

# **Breakthrough Solutions for Real-time Digital Systems Analysis**

As a digital design engineer, you're dealing with faster edge speeds and tighter timing margins that create more signal integrity issues than ever before.

The Tektronix TLA Family of logic analyzers delivers a wide range of powerful solutions. The TLA's iView capability enables you to observe how the digital and analog worlds interact. Connecting an external oscilloscope to your TLA delivers an integrated measurement solution that can capture and display both domains in a single time-correlated view.

For every task you face, the TLA's innovative MagniVu technology provides 125 ps timing resolution on all channels - all the time - through the same probe. Our industry-leading logic analyzers provide up to 800 MHz state acquisition with 1.25 Gb/s data rate for advanced processors and buses. And simultaneous state, high-speed timing and analog analysis pinpoints elusive faults.

The TLA Family also works with the world's first connectorless logic analyzer probes, only from Tektronix.

These high-performance, low-capacitance (0.7 pF total capacitance), active logic analyzer probes provide cleaner signals and reduce layout complexity and cost. The probes support both single-ended and differential signals with the same pattern.

This is the kind of performance you expect from Tektronix – with productivity and connectivity tools that will greatly shorten your time to market.

#### **Timing Resolution**

Whether you are debugging a high-performance computer or part of an embedded system, the timing parameters of your designs demand sub-nanosecond resolution. Logic analyzers that only offer 4 ns timing resolution are simply not adequate to capture today's complex problems. Nobody wants to trade off channels for resolution, buy separate timing modules, or trade up to more expensive hardware to get the resolution today's designs require. The TLA Family with MagniVu acquisition provides 8 GHz (125 ps) timing resolution on every channel.

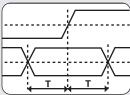

#### MagniVu Acquisition **Technology - A Breakthrough for Logic Analyzers**

The TLA Family includes a wide selection of logic analyzers with unprecedented measurement capabilities. At the heart is a breakthrough acquisition technology called MagniVu. MagniVu is a super-high-speed sampling architecture that dramatically changes the way logic analyzers work and enables them to provide startling new measurement capabilities.

#### **Capturing and Correlating Elusive Faults**

Complex system problems, especially intermittent ones, that show up late in product development can derail the most carefully planned schedules. TLA logic analyzers keep embedded hardware and software designers on track by providing a non-intrusive tool to monitor, capture and analyze these elusive real-time system problems. By capturing and correlating multiple views of data, including analog, digital and embedded software, the design team can quickly identify the source of a problem, wherever it is.

# **World's Fastest Logic Analyzer**

These remarkable, high performance logic analyzer modules plug into your existing Windows 2000 Professional logic analyzer mainframe to deliver unmatched accuracy, speed, and ease-of-use for debug and verification work. You may also route the analog signal of any 4 logic analyzer channels to an oscilloscope. And all of the modules offer PowerFlex customer-installable memory and speed upgrades to satisfy future needs.

► Detailed Product Information

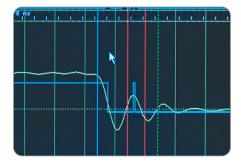

# Find Digital Signal Integrity Problems

Faster edge speeds and tighter timing margins are creating more signal integrity issues than ever before. Overshoot, ringing, crosstalk, reflections and ground bounce can cause glitches and intermittently alter the timing of otherwise stable signals.

Connecting an external digitizing oscilloscope to your TLA system with Integrated View capability provides up to 6 GHz analog signal bandwidth, along with the hundreds of logic signals you are already monitoring. Since the external Tektronix digital oscilloscope data is automatically time-correlated, the iView capability lets you easily observe the quality of critical signals alongside the original behavior they affect.

### **Probing Solutions**

Whether you are building high-density test connectors into your verification platform, using a configured probe adapter for popular microprocessors or buses, or just hooking up signals as you need more visibility, Tektronix has the probing solution.

# Digital and Analog Through a Single Probe

Here is an innovation the world of test and measurement has needed: simultaneous analog and digital measurements through a single logic analyzer probe. No more having to get out your oscilloscope probe for analog information. Now, one probe does it all. You get quick signal access, with no double-probing, no double-loading, and no more trying to handle two probes at once. Nothing is easier, or yields cleaner signals.

Digital/analog overlay.

# P6860/80 Connectorless Logic Analyzer Probes

Tektronix offers a family of new high-performance, low-capacitance, active logic analyzer probes which do away with add-on connectors and attach directly to printed circuit boards. These connectorless probes use Silicon Germanium (SiGe) technology to provide high-quality signal measurements.

#### Stimulus for Functional Verification

System verification often requires you to stimulate your designs with ideal or faulty digital patterns. The TLA pattern generator controls your circuit at full speed or steps through individual states. With the combination of logic analyzer and pattern generator modules, you can control and monitor real-time system operation.

### The Integrated View

Today almost every design is a high-speed design, with fast clock edges and data rates on even the most common IC devices. So nearly every design requires signal integrity analysis. Engineers need to see the analog characteristics of high-speed digital signals in relation to complex digital events in the circuit. The solution: iView.

The iView (Integrated View) capability seamlessly integrates data from Tektronix TLA logic analyzers and TDS oscilloscopes allowing designers to transfer analog waveforms from the oscilloscope to the logic analyzer display and automatically time-correlate them. The result: engineers can quickly track down elusive signal integrity problems in their designs.

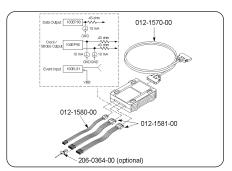

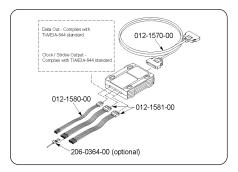

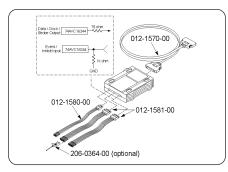

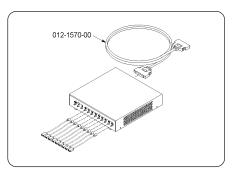

The new iView package includes TLA Application Software and an interconnect cable to integrate TLA600 or TLA700 Series logic analyzers with a wide range of external TDS Series oscilloscopes. iView capability couples selected Tektronix TDS family oscilloscopes with TLA Series logic analyzers, producing a solution that shows, on the same logic analyzer display, time-correlated views of both digital and analog waveforms.

Set up is easy through the use of an external oscilloscope "wizard" in the TLA Series logic analyzer user interface that guides the user through set up and connection. No user calibration or calibration fixture is required. And, once set up is completed, the iView capability is completely automated.

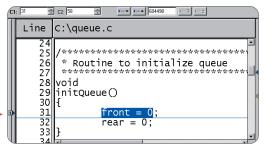

# Find and Analyze your Difficult Real-time Software Problems

Source code debugging.

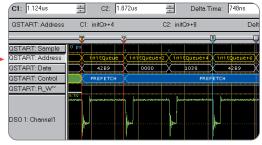

| Sample     | Q-Start<br>Address         | Q-Start<br>Data | Q-Start<br>Mnemonic                           |              |

|------------|----------------------------|-----------------|-----------------------------------------------|--------------|

| 136<br>143 | StopLite+32<br>StopLite+3C | 23FC<br>23FC    | MOVE.L #00001001,stopLights+10                | ( <u>s</u> ) |

| 150        | StopLite+46                | 4EB9            | MOVE.L #00000401,stopLights+14  JSR initQueue | (S)<br>(S)   |

| 158        | initQueue                  | 42B9            | CLR.L front                                   | (s)          |

| 161        | initQueue+6                | 42B9            | CLR.L rear                                    | (s)          |

| 166        | initQueue+C                | 4E75            | RTS                                           | (S)          |

| 172        | StopLite+4C                | 7E00            | MOVEQ #00000000,D7                            | (S)          |

| 170        | Stanlital/E                | 2007            | MOVE I D7 D0                                  | (0)          |

► Real-time instruction trace.

Real-time correlation to hardware.

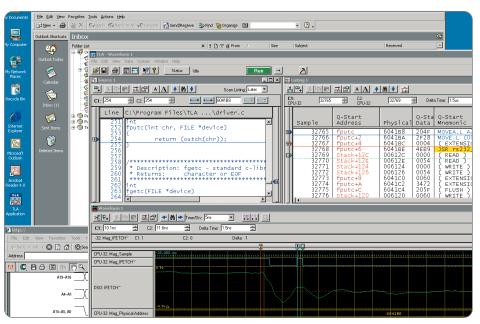

### Source Code Debugging

Tektronix logic analyzers provide real-time debug visibility by nonintrusively capturing instruction execution and system signals. This maximizes source code debugging productivity by linking the source code to instruction trace history, correlated to system hardware signals.

#### **Real-time Instruction Trace**

TLA software includes disassembly capability for analyzing every bus transaction and determining what instructions were read across the bus. The software then places the assembly mnemonic in the display with the associated address. This disassembly display enables you to view the data at different levels of abstraction.

The state display provides a view of raw hex data. The hardware display shows every bus cycle type with instructions. The software display filters out the noninstruction cycles. The flow control shows only instructions that cause a change in the program flow, and the subroutine display shows only the entry and exit points to subroutines.

### **Real-time Correlation** to Hardware

With the TLA's time stamp always running, every acquisition and every bus cycle has a unique 125 ps time stamp. Because of this capability, the TLA700 Series provides precision time correlation across ALL the modules in the TLA700 system, even across expansion mainframes. This allows you to see how the event on one bus affects the operation of another bus in the system.

► Detailed Product Information

#### **Processor Support**